| USN | 1. 43    |     |  |  |  |     |

|-----|----------|-----|--|--|--|-----|

| 11  | 2 1 . 35 | 375 |  |  |  | 100 |

## NEW SCHEME

## Fifth Semester B.E. Degree Examination, Dec. 06 / Jan. 07 Electrical and Electronics Engineering

## Operational Amplifier and Linear IC's

Time: 3 hrs.]

[Max. Marks:100

Note: I. Answer any FIVE full questions.

- 2. Missing data may be suitably assumed.

- 3. Use of Op-amp data sheets is permitted.

- 1 a. Define the following electrical parameters for an op-amp:

- i) Input off-set voltage ii) Input resistance iii) Output voltage swing iv) CMRR.

(08 Marks)

- b. What information does transfer curve reveal about op-amp? (84 Marks)

- Sketch the circuit of a capacitor-coupled voltage follower. Explain the design procedure. (08 Marks)

- Define: i) Loop phase shift ii) Loop gain iii) Open-loop-gain iv) Closed loop gain for a feed back system.

(08 Marks)

- What is frequency compensation? Explain phase lag or phase lead compensation method. (08 Marks)

- List the precautions that should be observed for op-amp circuit stability. (04 Marks)

- 3 a. The maximum output voltages of each of the voltage comparators shown in fig.3(a) are ±15 V. Sketch the output waveforms for each when V<sub>in</sub> is a 10 V peak sine wave. In each case show V<sub>in</sub> and V<sub>o</sub> and label voltage levels where switching occurs.

06 Marks)

7K 7

+12 0

Fig.3(a)

- b. Sketch and explain the working of sample and hold circuit. (06 Marks)

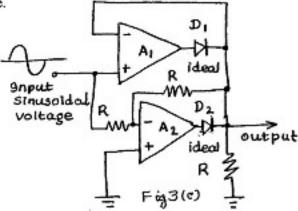

- Name the op-amp circuit shown in fig.3(c) and explain its working and sketch its transfer curve. (08 Marks)

Contd.... 2

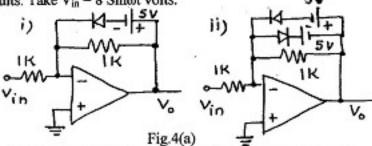

a. Referring to fig.4(a) sketch the output and transfer curve for the given op-amp clipper circuits. Take V<sub>in</sub> = 8 Sinot volts.

- Sketch positive clamper circuit using op-amp and explain its operation. (08 Marks)

- Sketch the circuitry of an astable multivibrator using op-amp and sketch the relevant waveforms. (10 Marks)

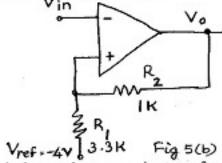

- The output of the Schmitt trigger shown in fig.5(b) switches between +10 V and -10 V.

- i) Find the lower and upper trigger levels ii) Find hysterisis iii) Sketch the hysterisis loop iv) Sketch the output when V<sub>in</sub> is a 10 V peak sine wave. (10 Marks)

- 6 a. Define an oscillator and what are the two requirements for oscillation. (03 Marks)

- Sketch Wein Bridge oscillator circuit and derive expression for the:

- i) frequency of the waveform generated and ii) gain required for sustaining oscillations. (12 Marks)

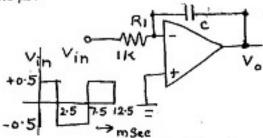

- c. Sketch the output of an integrator shown in fig.6(c) on the graph sheet. Take R<sub>1</sub> = 1 K, C = 0.1 µF. (05 Marks)

Fig.6(c)

- Derive expression for gain and phase angle of first order low pass Butterworth filter.

(08 Marks)

- b. What is a phase locked loop? Explain the working of building blocks of PLL.

(08 Marks)

- c. What is a dc voltage regulator? Define: i) line regulation ii) load regulation.

(04 Marks)

- 8 a. Sketch the circuit of a voltage follower regulator. Explain its operation. (06 Marks)

- Sketch the basic circuit of 723 voltage regulator and explain the regulator action.

(10 Marks)

- Differentiate small signal amplifiers and power amplifiers. (04 Marks)